Introduction

Nanocomputing is a recent research branch which is carried on at the VLSI Lab. The main goal is to investigate how to overcome the limitations of current computational systems by exploiting the possibilities offered by emerging technologies and unconventional architectures. The end of Moore’s Law and the scaling of MOS transistors has lead to the development of a huge number of new technologies. The nature of these technologies is often very different from transistors. As a consequence old architectural concepts cannot be applied effectively to these new technologies.

When studying emerging technologies the research cannot stop at the device level. To understand the limitations of a new device it is necessary to design complex and realistic circuits. Only at this point, it is possible to understand the effectiveness of a new technology. The reason is quite simple: parameters like speed and power consumption can be evaluated accurately only at the system level. The outcomes of designing a new architecture based on a new technology are two. First, it is possible to understand the performance of that technology. Second, it highlights the strength and the limitations of such technology. It is, therefore, possible to go back at the device level and modify the device itself to solve the issues found.

This methodology is the key point of the research carried on at the VLSI lab. Device and architectures are studied together creating a positive loop that brings to the enhancement and to the discovery of new technologies and architectures.

Unconventional architectures

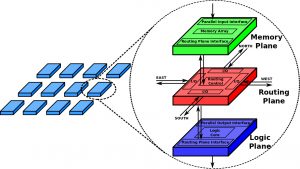

The Von Neumann architecture is the back-bone of most of modern computational systems. In this model logic and memory are two separated entities. This architectural model was successfully employed throughout the entire history of electronics. It is a model that worked very well especially in conjunction with the scaling of transistors. However it is now showing all its limits because the logic part is much faster than the memory, so the performance is bottlenecked by the memory. The aim of this research branch carried on at the VLSI group is twofold: to study new kind of architectures, free from the limitations of the Von Neumann model, and to successfully exploit emerging technologies. Parallelism and massive parallelism, logic-in-memory, and brain-inspired computation are all keywords that we follow in developing these new “unconventional architectures”.

Since the limitation is the interaction with the memory, the successful implementation of the logic-in-memory or in-memory computing principle can be the key to the future development of computational systems. A circuit where logic and memory are merged into one single entity does not suffer from bandwidth limitations or similar problems. To successfully implement logic-in-memory circuits it is possible to employ new technologies where the device behaves both as a logic and memory element. Parallelization, memory locality, and 3-dimensionality are instead exploited to design circuits where memory is physically located near the logic units. Finally, the brain is taken as inspiration for its efficiency in both power consumption and parallelization.

The end of MOS scaling process as generated an incredibility number of new technologies that are currently under development. Many of them are profoundly different from transistors in both their physical structure and their behavior. If the same old architectures are used in combination with emerging technologies the results may be much different from what obtained with MOS transistors. An example can be done using field coupled devices, where the fastest adder is the ripple carry adder that is the slowest adder in MOS technology. The aim of this part of the research is the development of new architectures adapted to the characteristics of each new technology.

Emerging Technologies

Once was clear that the scaling of transistors was reaching its limit, researcher started to study new technologies able to overcome these limits. These technologies are generally called emerging technologies. They can be roughly divided into 4 macro-categories, spintronic devices, molecular and atomistic devices, resistive devices and advanced transistors. The research carried on at the VLSI covers mainly spintronic devices, molecular devices, and advanced FET devices.

Spintronics

Spintronic is a branch of electronics that deals with spin-polarized currents. The discovery of spintronics was the breakthrough the lead to modern high-density hard drives and the newly developed magnetic RAMs. There are two main devices at the base of spintronics, GMRs (Giant Magneto-Resistances) and MTJs (Magneto-Tunnel Junctions). Both can be seen as variable resistances where the resistance value depends on the magnetic state of the device.

While GMR and MTJ are commercially available devices, a big number of other devices has been investigated at research level. Some of these devices are currently studied at the VLSI lab, like NanoMagnet Logic (NML) and perpendicular NML (pNML). These new devices are interesting because they offer features not available in MOS-based circuits, like the ability to combine memory and logic on a single device, the intrinsic ability to fabricate 3D circuits and no standby power consumption. A recently developed branch of this research has led to the development of the Racetrack Logic, Logic-in-Memory devices based upon racetrack memories. A racetrack logic element can be seen as a memory element that is also able to perform logic operations on the stored information.

Molecular devices

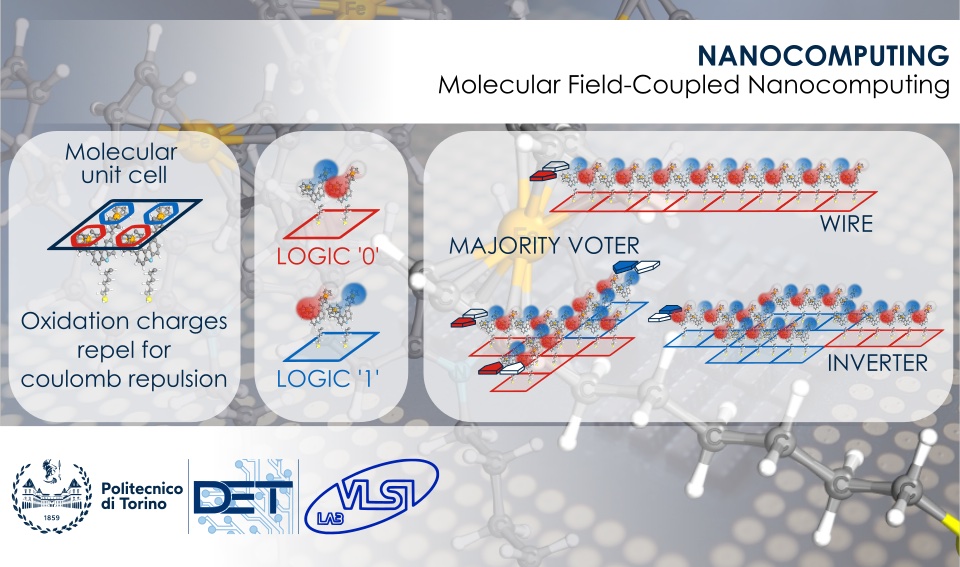

This research studies Molecular Field-Coupled Nanocomputing (FCN). It encodes the information in the polarization of single molecules according to the Quantum-dot Cellular Automata (QCA) paradigm and propagates it through local intermolecular electrostatic interactions. Molecular FCN permits the implementation of nanoscale logic gates for THz and low-power digital electronics. Quantum mechanics effects dominate molecular behavior. Therefore, ab initio techniques are widely employed to study static and dynamic molecular behavior. Then, simulation results are used to develop models for the simulation and design of complex circuits. The research developed algorithms for the fast simulation of molecular FCN devices to understand the potential of molecular FCN, favoring the realization of design methodologies and studying the integration of molecular FCN with CMOS technology. Several applications are addressed, such as digital computing, logic-in-memory and neural computing. Finally, the research addresses a concrete prototype’s experimental fabrication and characterization.

Goals

- Investigation of molecule characteristics necessary to accomplish Molecular FCN digital electronics with the aim of engineering future molecules

- Development of models of Molecular FCN devices and circuits and evaluation of Molecular FCN electronics characteristics such as power, speed and area

- Study and realization of a Molecular FCN device prototype

- Integration of Molecular FCN circuits with CMOS through readout systems

- Realization of algorithms for simulation and design tools integrated into the ToPoliNano suite

Design of Molecular FCN circuits and systems for the technology assessment

References

- Ardesi, Y., Garlando, U., Riente, F., Beretta, G., Piccinini, G., & Graziano, M. (2022). Taming Molecular Field-Coupling for Nanocomputing Design. In ACM Journal on Emerging Technologies in Computing Systems (Vol. 19, Issue 1, pp. 1–24). Association for Computing Machinery (ACM).

- Beretta, G., Ardesi, Y., Graziano, M., & Piccinini, G. (2022). Multi-molecule field-coupled nanocomputing for the implementation of a neuron. IEEE Transactions on Nanotechnology, 21, 52-59.

- Ardesi, Y., Wang, R., Turvani, G., Piccinini, G., & Graziano, M. (2020). SCERPA: A Self-Consistent Algorithm for the Evaluation of the Information Propagation in Molecular Field-Coupled Nanocomputing. In IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (Vol. 39, Issue 10, pp. 2749–2760). Institute of Electrical and Electronics Engineers (IEEE).

- Ardesi, Y., Beretta, G., Vacca, M., Piccinini, G., & Graziano, M. (2022). Impact of Molecular Electrostatics on Field-Coupled Nanocomputing and Quantum-Dot Cellular Automata Circuits. In Electronics (Vol. 11, Issue 2, p. 276). MDPI AG.

Methodology

- Physical and mathematical modelling (MATLAB)

- Density Functional Theory (DFT) and Real-Time Time-Dependent DFT (RT-TDDFT) calculation (ORCA and QuantumATK)

- Molecular Dynamics (MD), Ab Initio Molecular Dynamics (AIMD) calculation (LAMMPS, ORCA)

- Finite-Element Modelling (ELMER)

- Software development

- ToPoliNano

Link

- SCERPA: https://zenodo.org/record/7457038

ERC Sector

- PE7_3 Simulation engineering and modelling

- PE7_4 (Micro and nano) systems engineering

- PE7_5 (Micro and nano) electronic, optoelectronic and photonic components

- PE3_12 Molecular electronics

Keywords

Molecular Computing, Quantum Cellular Automata, Molecular Electronics

FET devices

While there is nowadays little room for improvements of MOSFET technology. Other types of transistors are studied to continue, if possible, the development of transistor-based circuits. Some of these devices are now already in production, like FinFET transistors, others are still at the research phase, lige Gate All Around (GAA) transistors. These kind of devices maintains the characteristics of FETs but, thanks to a slightly different structure, they can be scaled a little bit beyond the limitation of traditional FETs.

![]()

At the VLSI lab these kind of devices are currently under investigations. The focus is mainly on FinFETs, GAAs, Silicon Nanowire transistors and Tunnel FETs. These devices are studied following the approach typically used in this lab: physical simulations and models are used in conjunction to understand the potential of a technology both at device and system level. This kind of technologies are studied with the help of TAMTAMS, an online tool that can be used to study and compare a transistor-like technology at device level and to estimate its performance at system level.